*This content has been reposted with the approval of the original author.

Everyone has played the single chip computer very well, and also rarely paid attention to VDD waveform. It is finished after the whole machine test is not abnormal. It is true that chip technology has been developing for many years, and chip ventors have also done enough work on chip reliability. Fluctuations in VDD generally do not affect the work of single chip microcomputer. However, as a careful and responsible electronic engineer, in daily development work, we should still know more about the MCU system designed by ourselves, and how its VDD waveform is. If there is abnormal fluctuation, the cause should be found and the risk should be evaluated. Some serious power down or fluctuation should be ensured by improving the circuit to ensure the reliability of the whole machine.

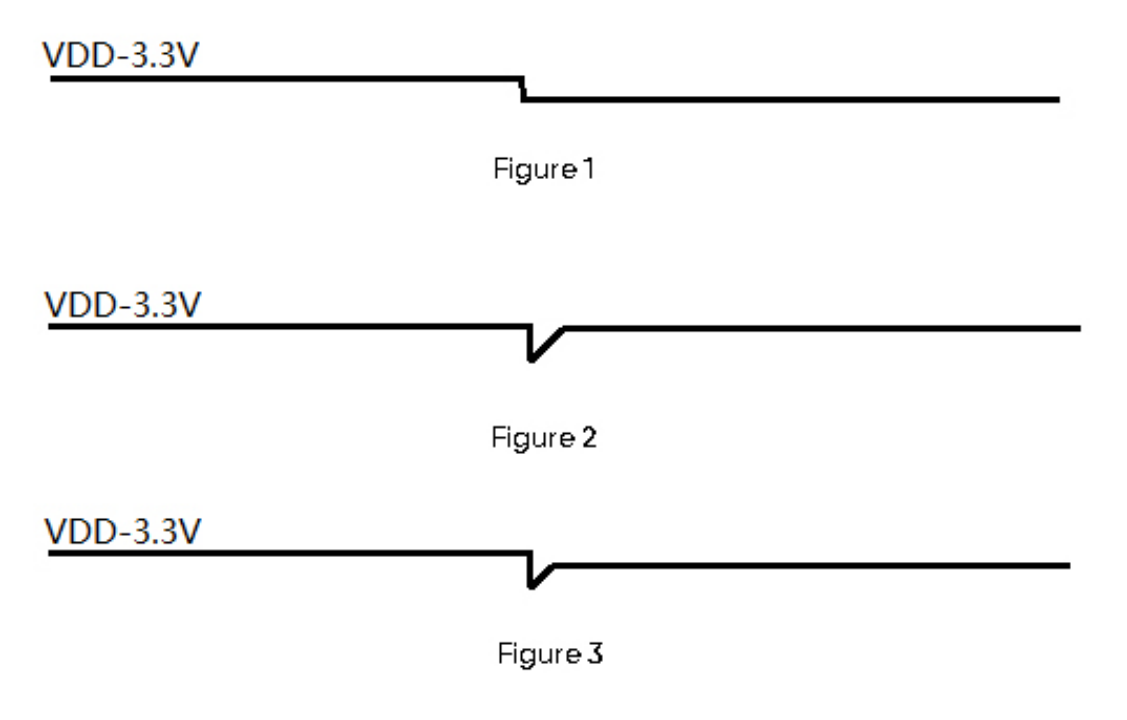

Three examples of VDD volatility are presented below. As shown in the following three figures (the concavity in Figure 2 and Figure 3 is us level), you can try to determine what is happening on the VDD and what “password” is transmitted by the VDD waveform.

In Figure 1, the VDD level is drawn down. Usually, in the VDD power supply domain, one (or some) modules or circuits run with large power consumption, that is, the overall demand current of the whole VDD domain increases, and the LDO or power output capacity of the VDD front end is limited (large internal resistance), and finally the VDD level is seen to decrease (you can use the resistance voltage divider model to understand).

In Figure 2, the VDD level is pulled down by tens to hundreds of us and then restored to the original level value. Usually in the VDD power supply domain, a (or some) module or circuit is connected or opened, and this module or circuit has a large capacitance, at the moment of access or open, the large capacitance is equivalent to a short circuit to the ground, the current is very large, the VDD level is pulled down; However, the power consumption of this module or circuit is not high, and the LDO or power output at the front end of the VDD can cope with it, so the VDD level is then restored to its original value.

In Figure 3, the VDD level is pulled down by tens to hundreds of us and then recovers below the original level value. Usually in the VDD power supply domain, a (or some) module or circuit is connected or

opened, and this module or circuit has a large capacitance, at the

moment of access or open, the large capacitance is equivalent to a

short circuit to the ground, the current is very large, the VDD level is pulled down; A certain (or some) module or circuit is operating with

high power consumption, that is, the overall demand current of the

whole VDD domain increases, while the LDO or power output capacity of the VDD front end is limited (large internal resistance), and finally see the VDD level decreased compared to before.

The above is just an example of the VDD waveform changes

actually provide a lot of key information, this information can let you better understand your own circuit, guide us to improve the

circuit, and improve reliability.

Next time you capture the waveform on VDD, you can analyze and think more about the “password” of VDD.