The MCU must have RTC Periodic Automatic Wake-up feature. Most of the projects that we will use this processor for are battery powered applications.

Therefore, it is critical that the MCU goes into minimum sleep mode, wakes up in millisecond resolution, performs the necessary operations and then goes back to sleep.

The datasheet of the APM32F030C8T6 MCU contains the following statement:

“It can be used for alarm and periodic wake-up in halt and standby mode.”

However, when we use the RTC alarm feature, the minimum wake-up time is 1 second. For our projects, 1 second is too long and does not meet our requirements. Do you have any suggestions for a solution for this issue?

RTC-Alarm have registers for Sub-second compare, and the clock source of RTC_Clock can be modified to, it comes from internal / external low speed clock(40kHz / 32.768kHz), divided by default {SPSC = 255, APSC = 127} .

When the RTC is not activate, those registers can be written.

The clock source of RTC [RTCCLK] can be LSE, LSI, or HSE/32.

In the case of LSE, RTCCLK is finally converted into calendar second pulse drive signal through 2-stage division:

First, it goes through the asynchronous divider unit at point A in the figure, with a default division factor of 128, forming the clock ck_apre.

By default, the frequency of this clock is 256Hz(3.9ms per step); then the clock pulse arrives at the synchronous divider unit at point B in the figure, with a default division factor of 256, ultimately forming a 1Hz second pulse to the calendar unit.

The configuration of the division factors of the two divider units is achieved by programming the relevant bits of the RTC_PSC register.

The asynchronous division factor configuration bit [APSC] has 7 bits, and the synchronous division factor [SPSC] has 15 bits.

In addition, the synchronous divider unit also includes a sub-second counter that counts in a countdown manner. Generally speaking, one counting cycle is 1 second, and its counting resolution or accuracy is [1/(SPSC+1)] second.

The sub-second register associated with it real-time records the counting value of the sub-second counter.

Obviously, with this sub-second counter, we can obtain a time of less than 1 second, or the decimal part of a second—sub-second, whose accuracy is determined by the synchronous division factor SPSC.

In summary:

- Sub-second is the term for time less than 1 second, ranging from 0 to 1 second, and is not a fixed value;

- The accuracy [resolution] of sub-seconds is adjustable and determined by the PREDIV_S parameter, i.e., [1/(SPSC+1)] second;

- The sub-second register [RTC_SUBSEC] real-time records the value of the sub-second counter, specifically reflected by SUBSEC [15:0];

- The sub-second time is calculated by the formula (SPSC-SUBSEC)/(SPSC+1). Note:There are three SUBSEC registers for Calendar/Timestamp/Alarm, now we are talking about Alarm.

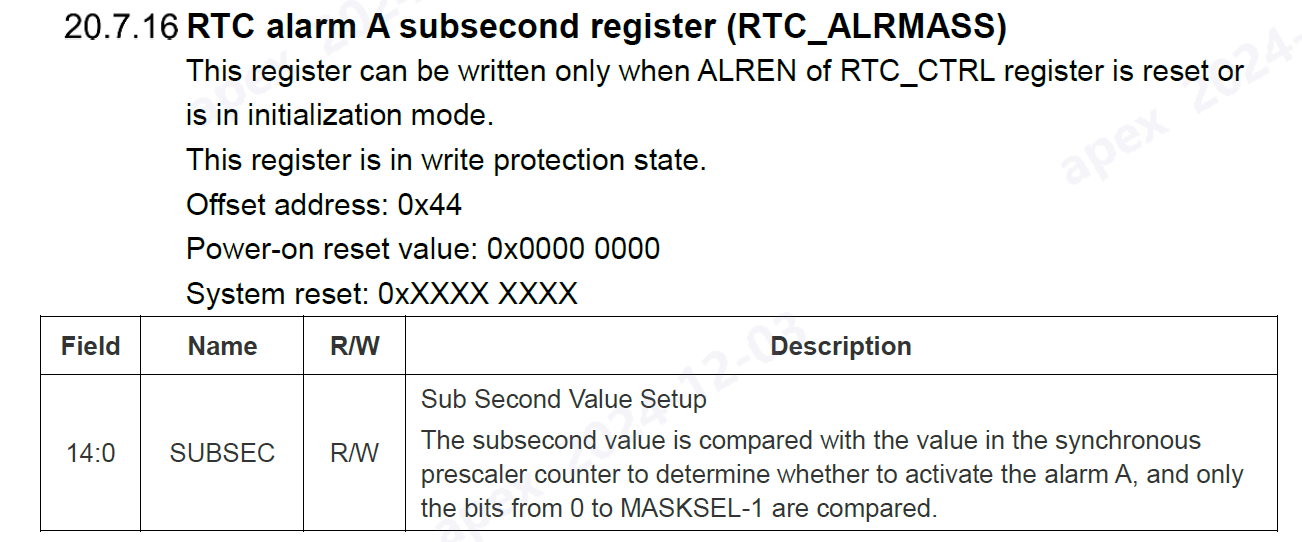

We are all familiar with the ALARM function of RTC, which involves setting a predetermined ALARM time and triggering an ALARM event and interrupt when the calendar time matches the set ALARM time.

The alarm condition for the ALARM time point can be configured in many flexible combinations.

For example, we can set an ALARM at a specific month, day, hour, minute, and second, or only set an ALARM at a certain minute and second while disregarding the rest, or set an ALARM only at a specific sub-second moment while disregarding the rest.

In the four ALARM settings shown in the above image, the gray areas indicate the aspects that are disregarded, meaning they are not involved in the comparison between calendar values and ALARM set values.

Here are the moments represented by each setting:

The first setting triggers an alarm whenever the hour, minute, and second in the calendar match the ALARM settings, without considering the rest.

The second setting triggers an alarm when the minute and second in the calendar match the ALARM settings, without considering the rest.

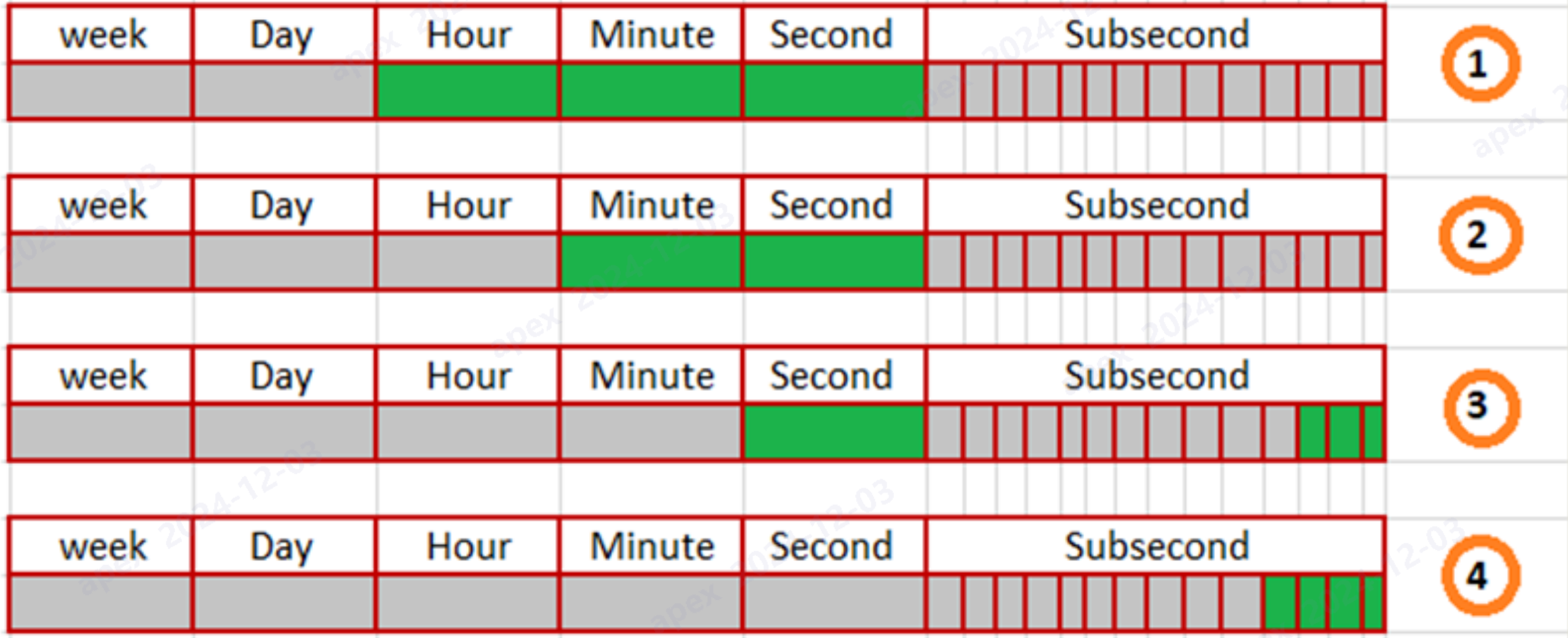

The third setting triggers an alarm when the second and the lower 3 bits of the sub-second in the calendar match the ALARM settings, without considering the rest.

The fourth setting triggers an alarm when the lower bits of the sub-second in the calendar match the ALARM settings, without considering the rest.

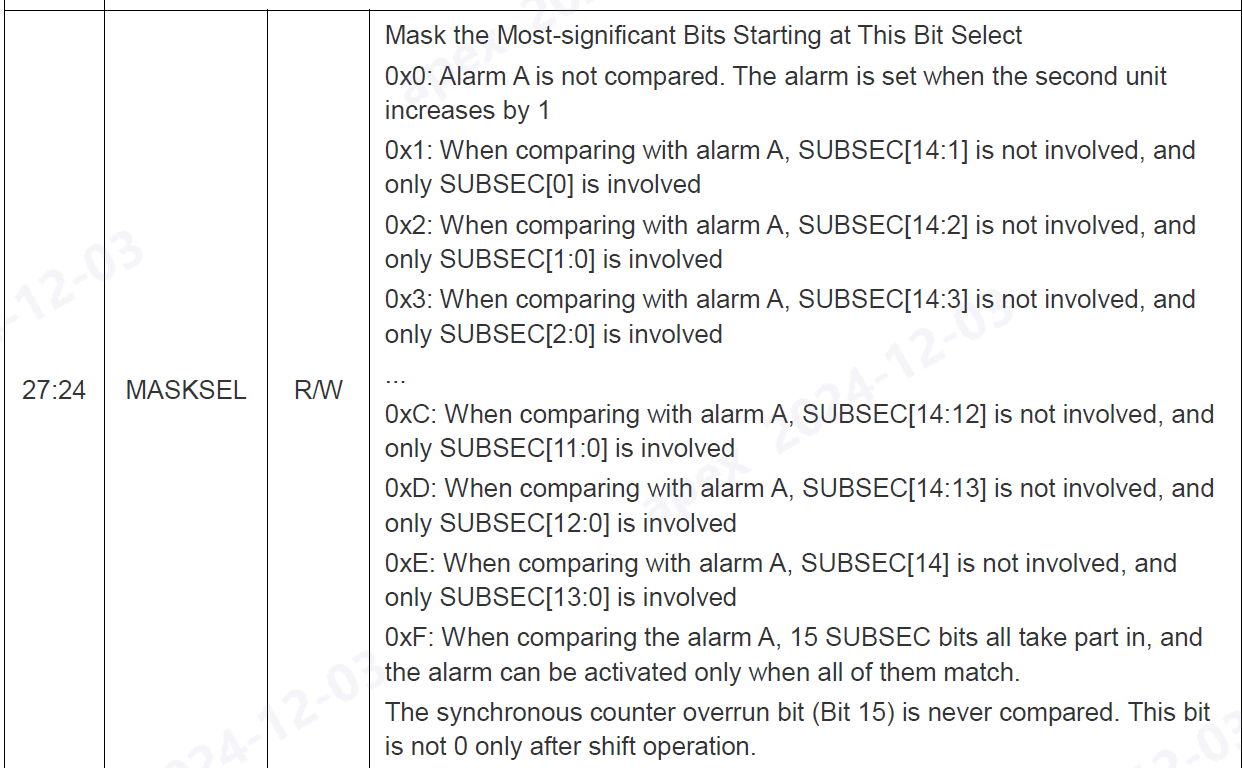

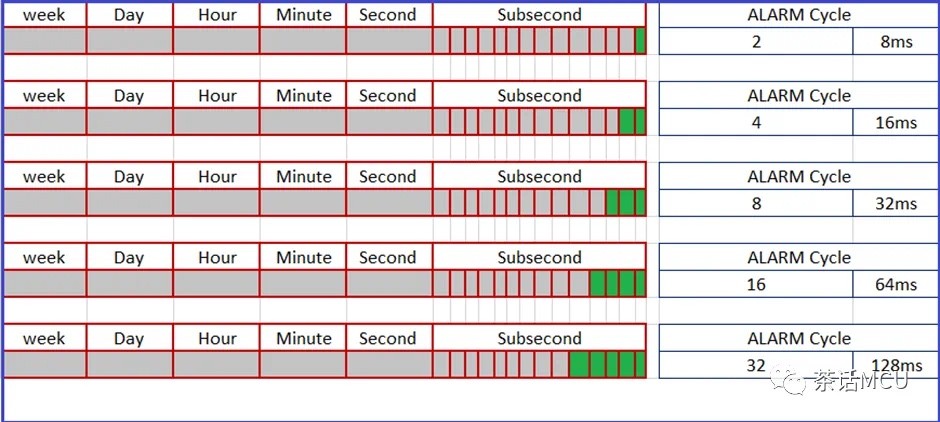

To mask the unwanted bits in SUBSEC register during compare, you can find MASKSEL register from RTC_ALRMASS. Only bits from 0 to MASKSEL-1 are compared.